xilinx ram ip 总结

在写rv cpu的过程中碰到ram选型的问题,因此起了这篇文章对网上的资料进行总结,顺便能解释之前fpga项目中例化bram时的怪相。

fpga中的ram分为两种,dram(lutram)和bram。

dram是指distributed ram,是利用fpga中的lut资源实现的ram。特点是,可以整合多个资源块中用剩下的lut,形成一整块逻辑上的ram,物理上不一定连续。

bram指block ram,是利用fpga中ram资源实现的ram。特点是,它是物理上连续的ram,一旦声明了一块bram,即使它占用的空间小于物理ram的最小容量,物理ram也会被完全占用,无法将多余的容量移作他用。因此bram十分消耗fpga的资源。

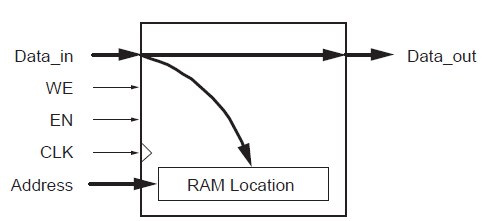

关于ram的分类,还需要注意的是,fpga中的这些ram都是指sram = Static Random-Access Memory,不同于dram = Dynamic Random Access Memory。sram的特点是,一旦读取数据,便会保持在输出端口,直到被更新。dram的特点是,读取数据以后,若不即时刷新便无法保持。

sdram,即通常我们所说的ddr,

下面将详细介绍lutram和bram的特性与区别。

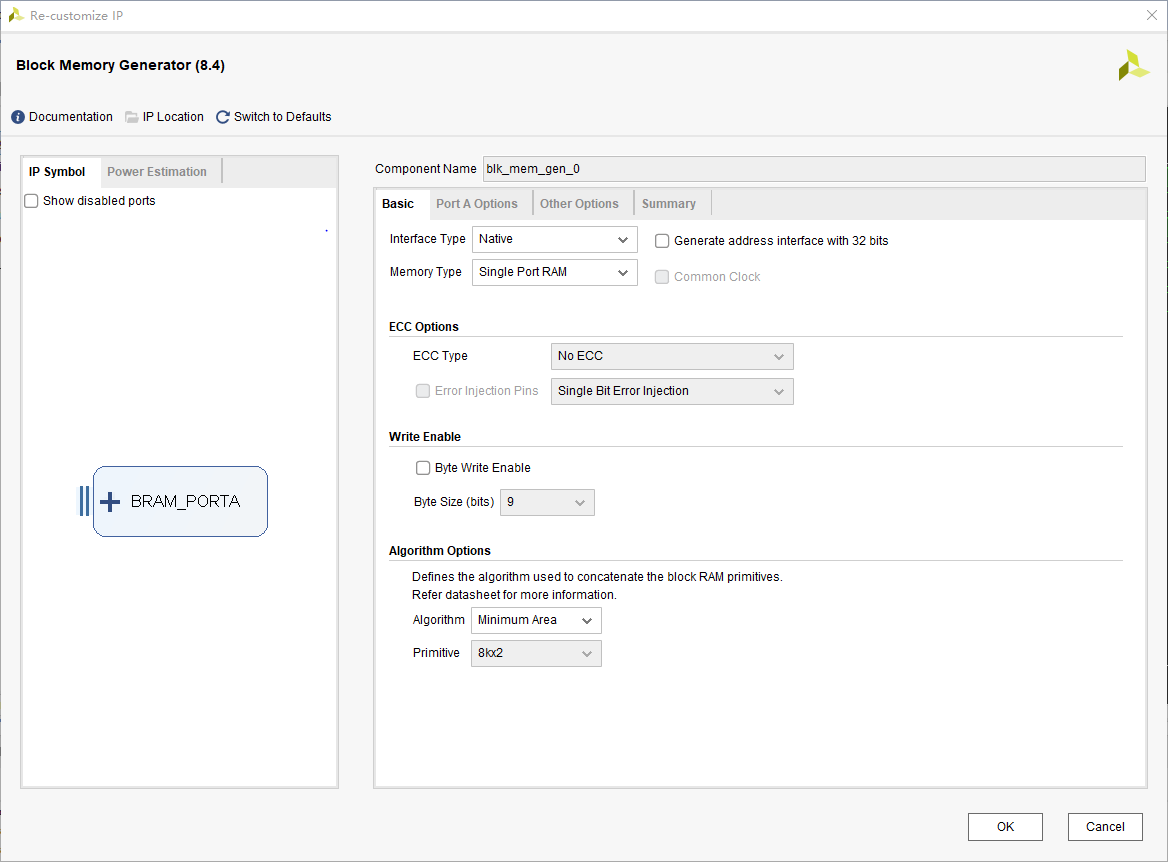

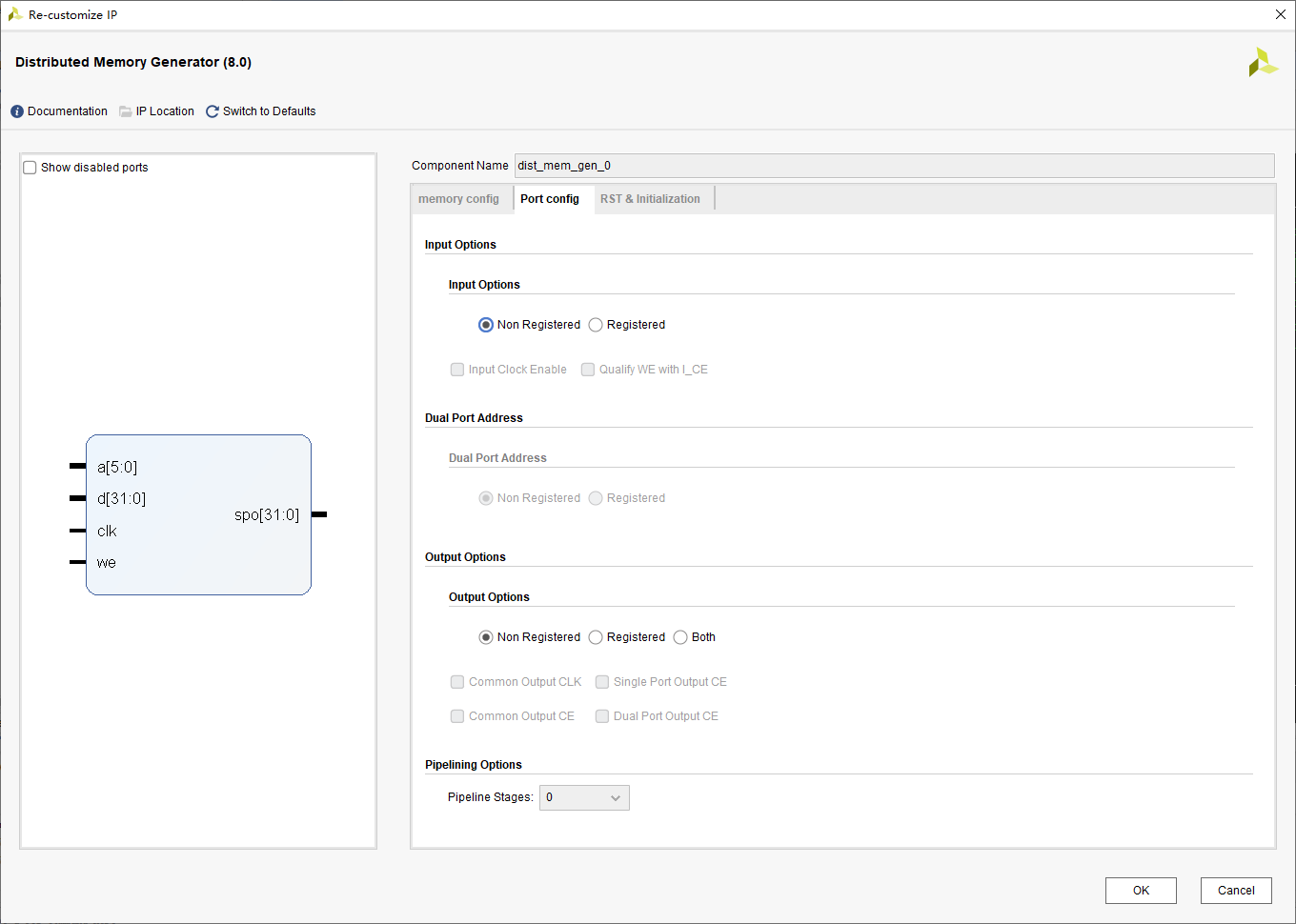

一、distributed ram ip

以单端口ram为例。

input默认非寄存器。

output如果勾选non-registered,那么在读写ram的时候,读数据会在地址更新后及时反应,没有延迟。需要注意的是,这个更新还是需要时钟触发的,同令输入地址更新的时钟。

如果勾选registered,那么在读写ram的时候,读数据会在地址更新后的下一个时钟反映。

此时,如果piplinestage为1,则读数据在地址更新后的下下个时钟反映。

值得注意的是,dram ip对于同一地址的操作,仅仅支持read first。

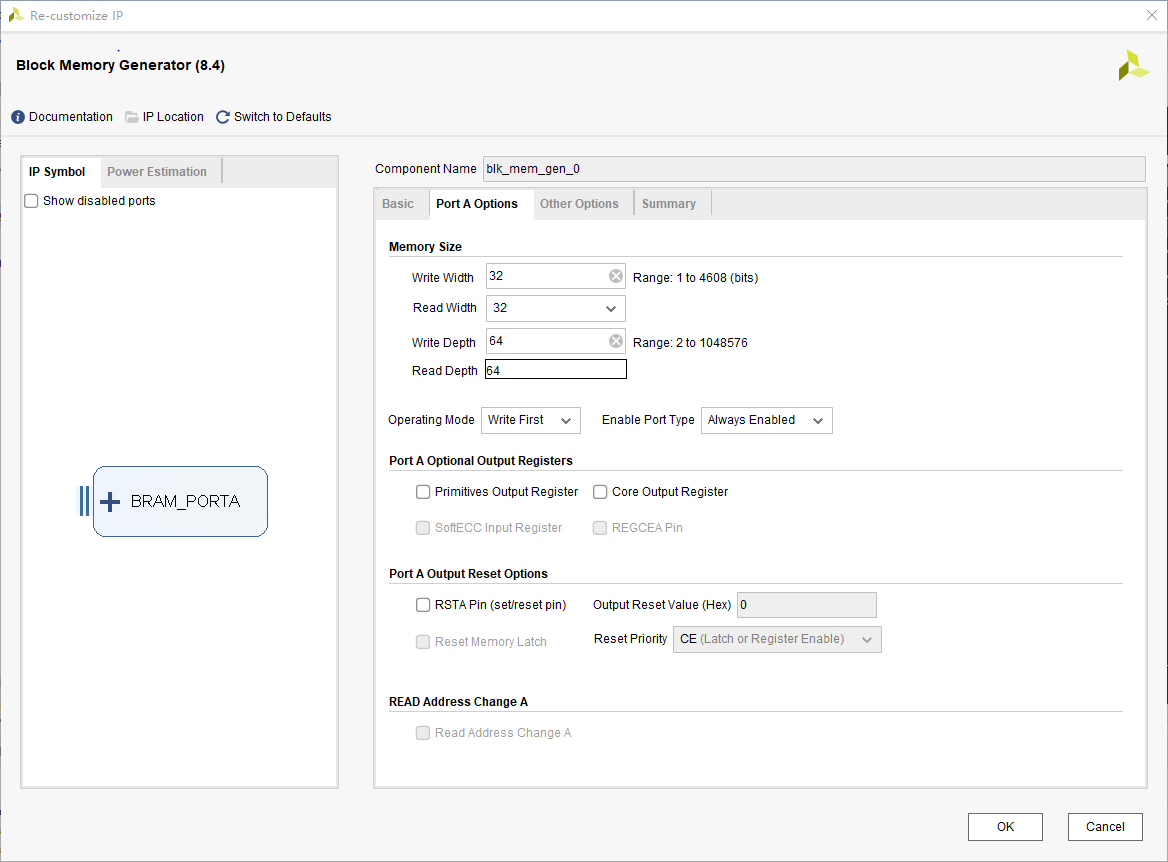

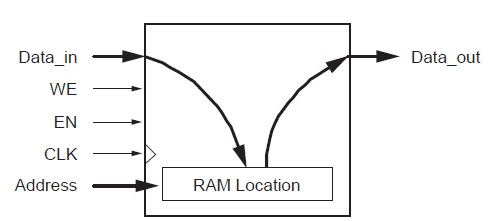

二、block ram ip

以单端口ram为例。

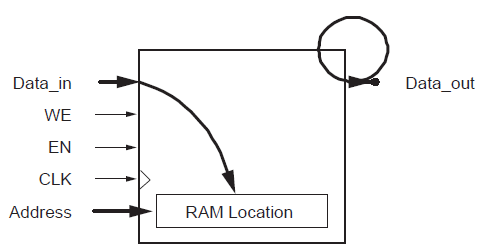

如果勾选primitives output register,那么在读写ram的时候,读数据会在地址更新后的下下一个时钟反映。

如果不勾选primitives output register,那么在读写ram的时候,读数据会在地址更新后的下一个时钟反映。

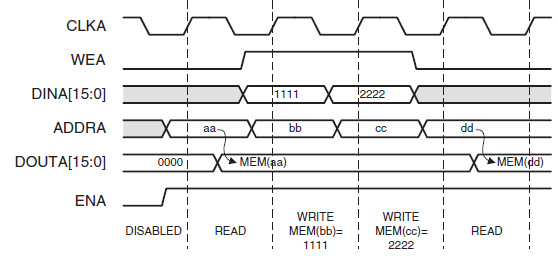

选择operating mode有三种情况,在读写同一地址时,对读出的数据有影响如下(假设不勾选primitives output register)

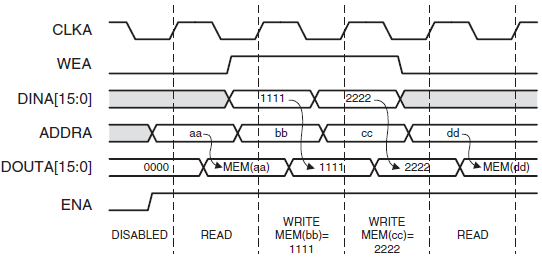

1.write first

这种情况下,读数据会在地址更新后的下一个时钟反映。并且得到上一个时钟写入的新数据。

也就是读写同一地址时,写数据在前,旧数据被丢弃。

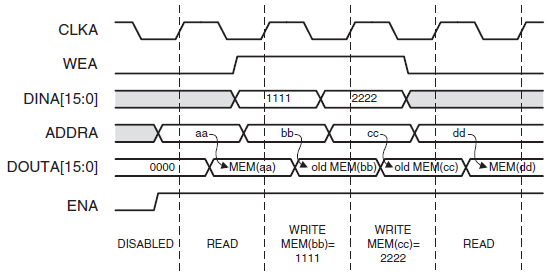

2.read first

这种情况下,读数据会在地址更新后的下一个时钟反映。并且得到上一个时钟写入z之前的旧数据。

也就是读写同一地址时,写数据在后,旧数据仅在下一个时钟可以被读出。

3.no change

这种情况下,读数据不会因为地址的变化而更新,直到write enable不使能。

之前项目遇到的问题是,bram写入数据和读出的数据不一致,虽然可以写入,但不完全一样。这种现象的原因是,勾选了byte write enable,同时wea并没有全部置为1,那么此时写入的数据就是不完全的。