《手把手教你设计CPU——RISC-V处理器篇》读书笔记(一)

前言

这篇文档,是书籍《手把手教你设计CPU——RISC-V处理器篇》的读书笔记,同时也是设计risc-v cpu软核的工作文档,记录了一些项目关键信息,知识框架和分析,服务于项目迭代需求,也对将来求职有帮助,算是个可讲的东西。

文档首先是回顾部分,这一部分将要提出关于riscv处理器的一些基本问题,并作出相应的解释回答,用于指导项目计划和进度。

一、回顾

1. risc-v 是什么?

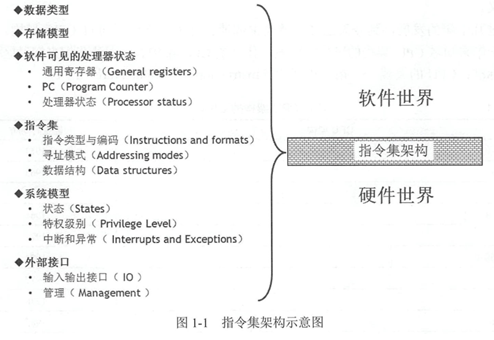

是一种指令集(ISA)。指令集分为RISC和CISC。

不同CPU的架构就是对指令集的不同实现,是指令集架构,也成为微架构(Microarchitecture)。如x86和MIPS、ARM。

处理器一般指完整的Soc。处理器核(Core)是指CPU当中最核心的部分,即CPU架构的物理实现。

指令集架构是计算机硬件与软件的接口。

risc-v是一种risc指令集。

2. risc-v具有什么特点?

开源免费,理念先进,定义了许多有助于突破业界产品性能瓶颈的特性。

3.为什么要学习risc-v?

对于嵌入式软件工程师,汇编级别的优化和对CPU架构的理解是必须的,这样才能提高调试能力,尽可能地利用好硬件的性能。目前,采取risc-v的mcu出货量巨大,不容忽视。

对于数字前端工程师,在工作中也可能接触到risc-v的软核,或是其他risc指令集软核。

对于初学者来说,设计一个CPU也是很好的入门数字IC的项目。

4.如何学习 risc-v?

首先看官方文档,看RISC指令集的内容,定义,指令编码特点。

自己动手,设计相应的硬件实现。

然后,用伯克利开源的工具和测试集(汇编)去验证硬件的功能。

5.risc-v的硬件实现包含哪些问题?

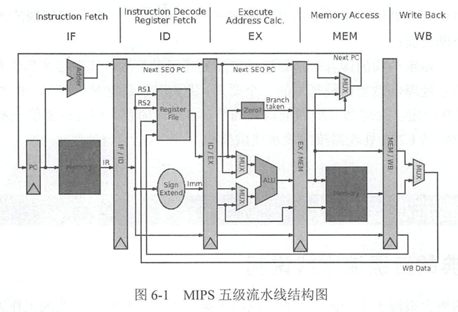

首先是,如何定义CPU的功能。要参考CPU架构的流水线模型。

一条指令的生命周期需要经过五个阶段

(1) 取指

从内存当中取出指令

(2) 译码

翻译指令,得到操作寄存器的索引,

根据索引,从通用寄存器组读写数据

(3) 执行

将数据写入操作单元(一般ALU)

(4) 访存

将操作结果写入内存,或者从内存读出某一地址的值。

(5) 写回

将指令执行结果写入通用寄存器组。数据源来自访存阶段或者执行阶段

第二个问题是,要如何为这五个阶段划分流水线。

具体实现时,需要划分数据通路和控制通路。数据通路为寄存器的流水线,以及控制寄存器读写的使能信号。控制通路则是根据逻辑生成控制寄存器的使能信号。

写CPU就是写控制逻辑。

6.衡量cpu性能的指标?

性能 = 执行时间的倒数。系统性能=空载系统的响应时间。

执行时间=响应时间,即开始一个任务到完成一个任务的时间。

吞吐率/带宽=给定时间内能完成的任务数量。

CPU性能=用户CPU时间,cpu用于用户程序的时间。

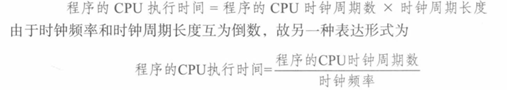

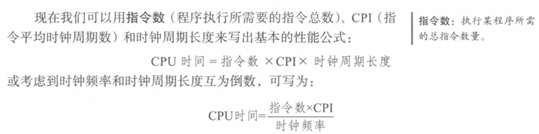

Cpu执行时间:

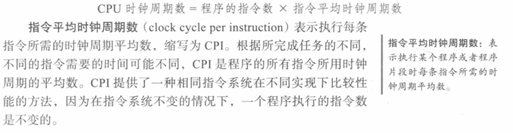

提高cpu性能,就要提高时钟频率,降低CPI。CPI有平均数,但是也随着指令的分布变化。

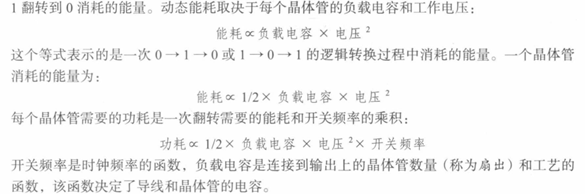

CMOS的主要能耗来自动态能耗:

升级cpu会降低工作电压,减少能耗。

MIPS随着程序改变,独立于性能发生变化,不适合用于度量性能。